A digitális hardver tervezési folyamata intenzíven átalakult az elmúlt években. Tehát a kis digitális áramkörök PAL-ok és PLA-k segítségével valósíthatók meg. Minden eszközt használnak különféle áramkörök megvalósításához amelyeknek nem kell több, mint az adott chipben kínált i / ps, o / ps és termékfeltételek száma. Ezek a chipek nem megfelelőek a meglehetősen szerény mérethez, általában legfeljebb 32 bemenet és kimenet kölcsönös számát támogatják. Ezen több be- és kimenetet igénylő áramkörök megtervezéséhez vagy számos PLA / PAL alkalmazható, vagy klasszikusabb típus chip használható CPLD-nek (komplex programozható logikai eszköz). A CPLD chip több áramköri blokkot tartalmaz egyetlen chipen, belső vezetékezési erőforrásokkal az áramköri blokkok rögzítésére. Minden áramköri blokk összehasonlítható egy PLA-val vagy egy PAL-tal.

Mi az a komplex programozható logikai eszköz?

A CPLD rövidítése: „Komplex programozható logikai eszközök”, ez egy egyfajta integrált áramkör hogy az alkalmazás-tervezők olyan digitális hardvereket terveznek, mint a mobiltelefonok. Ezek tudatosan magasabb terveket képesek kezelni, mint az SPLD-k (egyszerű programozható logikai eszközök), de kevesebb logikát kínálnak, mint az FPGA-k ( terepi programozható kaputömbök ). A CPLD-k számos logikai blokkot tartalmaznak, mindegyik blokk 8-16 makrocellát tartalmaz. Mivel minden logikai blokk egy adott funkciót hajt végre, a logikai blokk összes makrocellája teljesen összekapcsolódik. A felhasználástól függően ezek a blokkok összekapcsolódhatnak, vagy nem.

Komplex programozható logikai eszköz

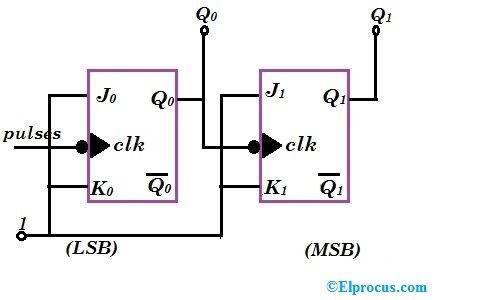

A legtöbb CPLD-ben (bonyolult programozható logikai eszközök) vannak makrocellák, logikai függvények összegével és választhatóval FF (flip-flop) . A chiptől függően a kombinatorikus logikai funkció 4-16 termékfeltételt támogat befogadó ventilátorral. A CPLD-k a váltási regiszterek és a logikai kapuk tekintetében is különböznek. Emiatt az FPGA-k helyett hatalmas számú logikai kapuval rendelkező CPLD-k használhatók. Egy másik CPLD specifikáció azt a termékkifejezést jelöli, amelyet egy makrocella képes végrehajtani. A termékfeltételek olyan digitális jelek termékei, amelyek egy meghatározott logikai funkciót hajtanak végre.

A CPLD-k több IC csomag űrlapban és logikai családban érhetők el. A CPLD-k a tápfeszültség, az üzemi áram, a készenléti áram és az energiaelvezetés tekintetében is különböznek. Ezenkívül ezek különféle memóriamennyiséggel és különféle memóriatámogatással érhetők el. A memóriát általában bit / megabitben fejezik ki. A memória támogatása ROM-ból, RAM-ból és kétportos RAM-ból áll. Ez magában foglalja a CAM-ot (tartalom címezhető memória), valamint a FIFO (első be, első kimenet) és a LIFO (utoljára be, utoljára) memóriát is.

Komplex programozható logikai eszköz architektúrája

Egy komplex programozható logikai eszköz programozható FB-k (funkcionális blokkok) csoportját tartalmazza. Ezen funkcionális blokkok be- és kimeneteit egy GIM (globális összekapcsolási mátrix) köti össze. Ez az összekapcsolási mátrix újrakonfigurálható, így módosíthatjuk a funkcionális blokkok közötti érintkezéseket. Lesz néhány bemeneti és kimeneti blokk, amelyek lehetővé teszik számunkra, hogy egyesítsük a CPLD-t a külvilággal. A CPLD architektúrája az alábbiakban látható.

Általában a programozható FB úgy néz ki, mint a logikai kapuk tömbje , ahol AND kapuk tömbje programozható és az OR kapuk stabilak. De minden gyártónak megvan a gondolkodásmódja a funkcionális blokk megtervezéséhez. A felsorolt o / p megtalálható az OR kapu kimeneteiből kapott visszacsatoló jelek működtetésével.

CPLD architektúra

A CPLD programozásban a tervet először Verilog vagy VHDL nyelven kódolják, amint a kódot szimulálják és szintetizálják. A szintézis során a CPLD modellt (céleszköz) válogatják, és elkészítik a technológián alapuló leképező háló listát. Ez a lista szoros lehet - az eredeti CPLD architektúrához való illesztés hely- és útvonal-folyamat segítségével, amelyet általában a CPLD Company sajátjának hely-és útvonal-szoftvere valósít meg. Ezután az üzemeltető elvégez néhány megerősítési folyamatot. Ha minden jó, akkor a CPLD-t használja, máskülönben átrendezi.

A CPLD építészeti kérdései

Ha egy komplex programozható logikai eszközt tervezünk, a következő architektúrával kapcsolatos kérdéseket lehet figyelembe venni

- A programozási technológia

- A funkcióblokk képesség

- Az I / O képesség

A CPLD különböző kiskereskedőkből származó családjai közé tartozik

- Altera MAX 7000 és MAX 9000 családok

- Atmel ATF és ATV családok

- Rács isp LSI család

- Rácsos (Vantis) MACH család

- Xilinx XC9500 család

A CPLD családjai

A CPLD alkalmazásai

A CPLD-k alkalmazásai a következőket tartalmazzák

- A komplex programozható logikai eszközök ideálisak nagy teljesítményű, kritikus vezérlő alkalmazásokhoz.

- A CPLD digitális tervezéskor használható a rendszerbetöltő funkcióinak végrehajtására

- A CPLD egy terepi programozható kaputömb konfigurációs adatainak betöltésére szolgál egy nem felejtő memóriából.

- Általában ezeket olyan kis tervezési alkalmazásokban használják, mint a cím dekódolása

- A CPLD-k gyakran használják sok alkalmazásban, például költségérzékeny, akkumulátorral működő hordozható eszközökben, alacsony mérete és alacsony energiafelhasználása miatt.

Így itt minden a bonyolult programozható logikai eszköz architektúráról és annak alkalmazásáról szól. Reméljük, hogy jobban megértette ezt a koncepciót. Továbbá, bármilyen kérdése van ezzel a koncepcióval, ill bármilyen elektromos és elektronikus projekt megvalósítására , kérjük, adja meg értékes javaslatait az alábbi megjegyzés részben kommentálva. Itt egy kérdés, mi a különbség a CPLD és az FPGA között?

Fotók:

- CPLD wikimedia

- A CPLD felépítése slidesharecdn