A JTAG (Joint Test Action Group) egy jól bevált IEEE 1149.1 szabvány, amelyet 1980-ban fejlesztettek ki az elektronikus kártyákon, ill. nyomtatott áramkörök . Ezt a technológiát arra használják, hogy elegendő teszthozzáférést biztosítsanak minden összetett kártyához, amikor a teszthozzáférés csökken. Így elindult a boundary scan technológia és a JTAG szabvány ill JTAG specifikáció alapítva. Az elektronika összetettsége napról napra növekszik, így a JTAG specifikáció vált a bonyolult és kompakt elektronikai egységek tesztelésének elfogadott tesztformátumává. Ez a cikk áttekintést nyújt a JTAG protokoll – alkalmazásokkal való munka.

Mi az a JTAG?

Az IEEE 1149.1 Standard Test Access Port és a Boundary-Scan Architecture név JTAG (Joint Test Action Group) néven ismert. Ezt a határellenőrzési architektúrát leginkább számítógépen belül használják processzorok mert az első JTAG-os processzort az Intel adta ki. Ez az IEEE-szabvány egyszerűen meghatározza, hogy a számítógép áramköreit hogyan tesztelik, hogy megbizonyosodjanak arról, megfelelően működik-e a gyártási eljárás után. Az áramköri lapokon teszteket végeznek a forrasztási kötések ellenőrzésére.

A Joint Test Action Group egy tűs nézetet biztosít a tesztelők számára minden IC-paddal, amely segít az áramköri lapon belüli hibák azonosításában. Miután ez a protokoll egy chiphez kapcsolódik, ez szondát tud csatlakoztatni a chiphez azáltal, hogy lehetővé teszi a fejlesztő számára a chip vezérlését, valamint annak más chipekkel való kapcsolatait. A Joint Test Action csoporttal való interfészt a fejlesztők is használhatják a firmware másolására egy elektronikus eszköz nem felejtő memóriájába.

Konfiguráció/Pin Out

A Joint Test Action Group 20 tűből áll, amelyek mindegyikét és funkcióit az alábbiakban tárgyaljuk.

Pin1 (VTref): Ez a cél referenciafeszültség érintkezője, amely a cél fő tápegységéhez való csatlakoztatásra szolgál, amely 1,5 és 5,0 VDC között van.

Pin2 (Vsupply): Ez az a céltápfeszültség, amelyet a cél 1,5 VDC – 5,0 VDC fő feszültségellátásának csatlakoztatására használnak.

Pin3 (nTRST): Ez egy teszt-visszaállító tű, amely a TAP vezérlő állapotgépének visszaállítására szolgál.

Tűk (4, 6, 8, 10, 12, 14, 16, 18 és 20): Ezek általános GND érintkezők.

Pin5 (TDI): Ez a tesztadatok a tűben. Ezek az adatok a céleszközbe kerülnek. Ezt a csapot meghatározott körülmények között fel kell húzni a céltáblán.

Pin7 (TMS): Ez a Teszt mód állapot tű, amelyet a rendszer a TAP vezérlő állapotgépének következő állapotának meghatározásához húz.

Pin9 (TCK): Ez egy tesztóra tű, amely szinkronizálja a belső állapotgép műveleteit a TAP vezérlőben.

Pin11 (RTCK): Ez az Input Return TCK tű, amelyet az adaptív órajelet támogató eszközökben használnak.

Pin13 (TDO): Ez a Test Data Out pin, így az adatok a céleszközről a Flyswatterbe kerülnek.

Pin15 (nSRST): Ez a Target System Reset tű, amely a cél fő reset jeléhez csatlakozik.

17. és 19. tűk (NC): Ezek nem csatlakoztatott tűk.

JTAG működik

A JTAG eredeti felhasználása határtesztelésre szolgál. Itt van egy egyszerű nyomtatott áramköri kártya, amely két IC-t tartalmaz, mint a CPU és FPGA . Egy tipikus kártya sok IC-t tartalmazhat. Általánosságban elmondható, hogy az IC-k sok érintkezőt tartalmaznak, amelyek sok csatlakozással vannak összekapcsolva. Itt, a következő ábrán csak négy csatlakozás látható.

Tehát ha sok táblát tervez, ahol minden táblának több ezer csatlakozása van. Ebben vannak rossz táblák. Tehát ellenőriznünk kell, melyik tábla működik és melyik nem. Erre tervezték a Joint Test Action Groupot.

Ez a protokoll használhatja az összes chip vezérlőtűjét, de a következő ábrán a Joint Test Action Group elkészíti a CPU összes kimeneti lábát és az FPGA összes bemeneti lábát. Ezt követően a CPU érintkezőiről bizonyos mennyiségű adat továbbításával és a tűk értékeinek az FPGA-ból történő kiolvasásával a JTAG kijelenti, hogy a PCB kártya csatlakozásai rendben vannak.

Valójában a Joint Test Action Group négy logikai jelet tartalmaz: TDI, TDO, TMS és TCK. És ezeket a jeleket meghatározott módon kell összekapcsolni. Először a TMS és a TCK párhuzamosan csatlakozik a JTAG összes IC-jéhez.

Ezt követően mind a TDI, mind a TDO csatlakoztatva van a lánc kialakításához. Amint láthatja, minden JTAG-kompatibilis IC tartalmaz 4 érintkezőt, amelyek a JTAG-hoz használatosak, ahol a 3 érintkezők a bemenetek és a 4. érintkezők kimenete. Az ötödik tű, mint a TRST, nem kötelező. Általában a JTAG tűket más célokra nem osztják meg.

A Joint Test Action Group használatával az összes IC határtesztet használ, amelynek eredeti okát a JTAG hozta létre. Jelenleg ennek a protokollnak a használatát kibővítették, hogy lehetővé tegye az FPGA-k konfigurálását, majd ezt követően a JTAG-ot az FPGA magban használják hibakeresési célokra.

JTAG architektúra

A JTAG architektúra alább látható. Ebben az architektúrában az eszköz mag logikája és a lábak közötti összes jel megszakad a BSR vagy Boundary Scan Register nevű soros letapogatási útvonalon. Ez a BSR különféle határellenőrző „sejteket” tartalmaz. Általában ezek a határpásztázó cellák nem láthatók, de használhatók teszt módban értékek beállítására vagy leolvasására az eszköz érintkezőiből.

A TAP-nak vagy Test Access Portnak nevezett JTAG interfész különböző jeleket használ a határellenőrzési műveletek támogatására, mint például a TCK, TMS, TDI, TDO és TRST.

- A TCK vagy a Test Clock jel egyszerűen szinkronizálja az állapotgép belső műveleteit.

- A TMS vagy a Test Mode Select jel mintavételezése a teszt órajel növekvő élén történik a következő állapot meghatározásához.

- A TDI vagy Test Data In jel a teszteszközbe tolódott adatot jelenti, különben a programozási logika. Ha a belső állapotú gép megfelelő állapotban van, akkor a mintavételezés a TCK növekvő élén történik.

- A TDO vagy a Test Data Out jel a teszteszköz eltolt adatait jelenti, különben a programozási logika. Ha a belső állapotú gép megfelelő állapotban van, akkor a TCK csökkenő élén érvényes

- A TRST vagy a Test Reset egy opcionális tű, amely a TAP vezérlő állapotgépének visszaállítására szolgál.

TAP vezérlő

A JTAG architektúrájában a teszt hozzáférési pont egy TAP vezérlőből, egy utasításregiszterből és tesztadat-regiszterekből áll. Ez a vezérlő tartalmazza a tesztelő állapotgépet, amely felelős a TMS és TCK jelek kiolvasásáért. Itt az adat i/p pin egyszerűen arra szolgál, hogy adatokat töltsön be az IC mag és a fizikai érintkezők közötti határcellákba, valamint adatokat töltsön be az egyik adatregiszterbe vagy az utasításregiszterbe. Az adat o/p láb a regiszterekből vagy a határcellákból származó adatok kiolvasására szolgál.

A TAP vezérlő állapotgépét a TMS vezérli, és a TCK órajelét végzi. Az állapotgép két útvonalat használ két különböző mód jelzésére, mint például az utasításmód és az adatmód.

Regisztrálok

A határellenőrzésen belül kétféle regiszter áll rendelkezésre. Minden kompatibilis eszköz legalább két adatregisztert és egy utasításregisztert tartalmaz.

Utasítási nyilvántartás

Az utasításregiszter az aktuális utasítás tárolására szolgál. Így az adatait a TAP vezérlő használja annak eldöntésére, hogy mit hajtson végre a kapott jelekkel. Leggyakrabban az utasításregiszter adatai írják le, hogy melyik adatregiszternek kell jeleket továbbítani.

Adatnyilvántartások

Az adatregiszterek három típusban állnak rendelkezésre: BSR (Boundary Scan Register), BYPASS és ID CODES regiszter. Ezenkívül más adatregiszterek is lehetnek, de ezek nem szükségesek a JTAG szabvány elemeként.

Boundary Scan Register (BSR)

A BSR a fő tesztelési adatregiszter, amelyet az adatok áthelyezésére használnak az eszköz I/O érintkezőire, illetve azok felé.

KITÉRŐ

A bypass egy egybites regiszter, amelyet a TDI – TDO-ból származó adatok átadására használnak. Így lehetővé teszi további eszközök tesztelését az áramkörön belül minimális rezsivel.

ID KÓDOK

Az ilyen típusú adatregiszter tartalmazza az eszköz azonosító kódját, valamint revíziószámát. Tehát ezek az adatok lehetővé teszik az eszköz csatlakoztatását a BSDL (Boundary Scan Description Language) fájljához. Ez a fájl tartalmazza a Boundary Scan konfigurációs részleteit az eszközhöz.

A JTAG működése kezdetben az az utasítási mód kiválasztása, ahol az „útvonal” üzemmód egyik állapota lehetővé teszi a kezelő számára, hogy egy TDI utasításon belül órajelet hajtson végre. Ezt követően. az állapotgépezet addig fejlődik, amíg át nem rendeződik. A legtöbb utasítás következő lépése az adatmód kiválasztása. Tehát ebben a módban az adatok TDI-n keresztül töltődnek be a TDO-ból való olvasáshoz. A TDI és TDO esetében az adatútvonalak az ütemezett utasításnak megfelelően lesznek elrendezve. Az olvasási/írási művelet elvégzése után az állapotgép ismét visszaállítási állapotba kerül.

Különbség a JTAG és az UART között

A JTAG és az UART közötti különbség a következőket tartalmazza.

| JTAG |

UART |

| A „JTAG” kifejezés a Joint Test Action Group rövidítése. | A ' kifejezés UART ” az univerzális aszinkron vevő/adó rövidítése. |

| Ez egy szinkron interfész, amely beépített hardvert használ a vaku programozásához . | Az UART egy aszinkron interfész, amely a memórián belül futó bootloadert használ. |

| Ez egy tesztport-készlet, amelyet hibakeresésre használnak, de használható firmware programozására is (amit általában megtesznek).

|

Az UART egy olyan típusú chip, amely az eszközökhöz, például mikrokontrollerekhez, ROM-hoz, RAM-hoz stb. irányuló kommunikációt vezérli. A legtöbb esetben ez egy soros kapcsolat, amely lehetővé teszi számunkra, hogy kommunikáljunk egy eszközzel. |

| Ezek négy típusban kaphatók: TDI, TDO, TCK, TMS és TRST. | Ezek kétféle hülye UART és FIFO UART változatban kaphatók. |

| A Joint Test Action Group egy soros programozási vagy adatelérési protokoll, amelyet mikrokontrollerek és kapcsolódó eszközök interfészében használnak. | Az UART egyfajta chip, különben a mikrokontroller alkomponense, amelyet egy aszinkron soros adatfolyam, például RS-232/RS-485 generálására szolgáló hardver biztosítására használnak. |

| A JTAG komponensei processzorok, FPGA-k, CPLD-k , stb. | Az UART komponensek CLK generátor, I/O shift regiszterek, adási vagy vételi pufferek, rendszer adatbusz puffer, olvasási vagy írási vezérlő logika stb. |

JTAG protokollelemző

A JTAG Protocol Analyzer, mint például a PGY-JTAG-EX-PD, a protokollanalizátorok egy fajtája, amely magában foglal néhány olyan funkciót, amelyek rögzítik és hibakeresik a kommunikációt a gazdagép és a tesztelés alatt álló tervezés között. Ez a típusú analizátor a vezető műszer, amely lehetővé teszi a tesztelő és tervező mérnökök számára, hogy teszteljék a JTAG egyedi tervezését a specifikációinak megfelelően a PGY-JTAG-EX-PD, például a Master vagy a Slave elrendezésével a JTAG forgalom generálására és a dekódoló csomagok dekódolására. Joint Test Action Group protokoll.

Jellemzők

A JTAG protokollanalizátor jellemzői a következők.

- Akár 25MH JTAG-frekvenciát támogat.

- Egyidejűleg generál JTAG forgalmat és protokoll dekódolást a buszhoz.

- JTAG Master képességgel rendelkezik.

- Változó JTAG adatsebesség és munkaciklus.

- Felhasználó által meghatározott TDI és TCK késleltetések.

- Gazdaszámítógép USB 2.0 vagy 3.0 interfész.

- Hibaelemzés a protokoll dekódolásán belül

- Protokoll dekódolt busz időzítési diagram.

- Folyamatos protokoll adatfolyam a gazdaszámítógépre a nagy puffer biztosításához.

- Protokoll tevékenységek listája.

- Különböző sebességeknél egy gyakorlati parancsfájl írható több adatkeret létrehozásának kombinálásához.

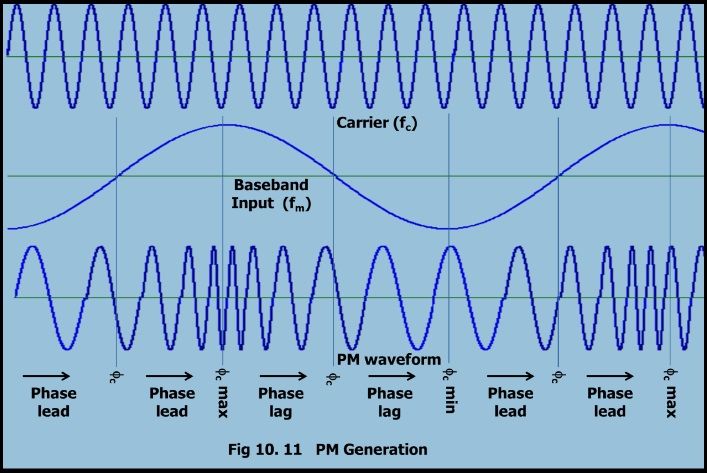

Időzítési diagram

Az a JTAG időzítési diagramja protokoll alább látható. A következő ábrán a TDO érintkező a nagy impedanciájú feltételen belül marad, kivéve a shift-IR/shift-DR vezérlő állapotát.

Shift-IR és Shift-DR vezérlő körülmények között a TDO tű frissítésre kerül a TCK csökkenő élén a Targeten keresztül, és mintavételezésre kerül a TCK növekvő élén a Host-on keresztül.

Mind a TDI, mind a TMS érintkezők egyszerűen mintavételezésre kerülnek a TCK növekvő élén a Targeten keresztül. Frissítve a csökkenő élen, különben TCK a gazdagépen keresztül.

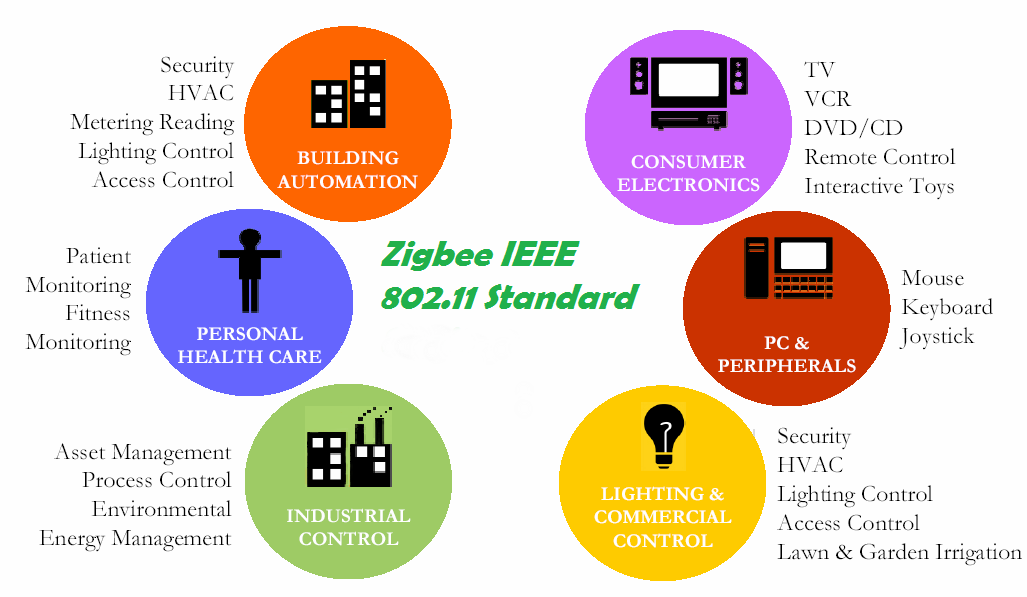

Alkalmazások

Az JTAG alkalmazások a következőket tartalmazzák.

- A Joint Test Action Group gyakran használatos a processzorokban, hogy belépési jogot biztosítson emulációs vagy hibakeresési funkcióikhoz.

- Minden CPLD és FPGA ezt használja interfészként, hogy hozzáférést biztosítson programozási funkcióihoz.

- A PCB-k fizikai hozzáférés nélküli tesztelésére használják

- Táblaszintű gyártási tesztekhez használják.

Tehát erről szól az egész a JTAG áttekintése – pin konfiguráció, alkalmazásokkal való munka. Az ipari szabvány JTAG-t a tervezés ellenőrzésére, valamint a gyártás utáni PCB tesztelésére használják. Itt egy kérdés, a JTAG jelentése?